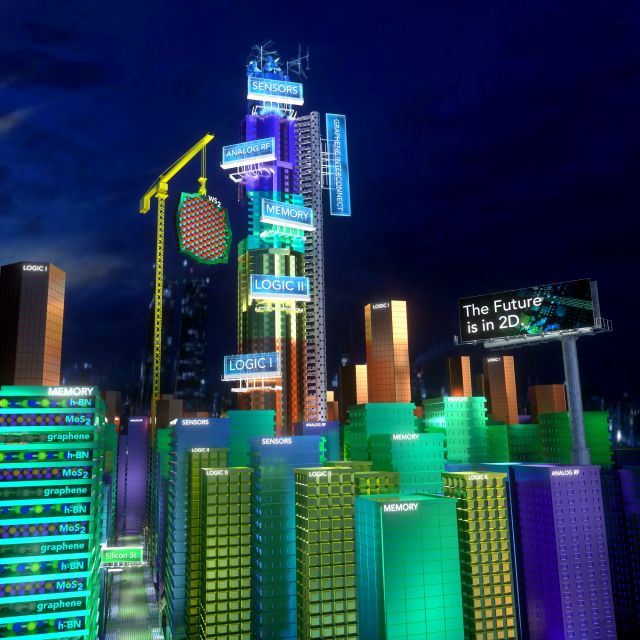

Saving Moore's Law: NRL Proposes 3D Integration with 2D

ECE Professor Kaustav Banerjee and researchers propose 3D integration with 2D materials

ECE Professor Kaustav Banerjee and researchers propose 3D integration with 2D materials

It’s a well-known observation: The number of transistors on a microchip will double roughly every two years. And, thanks to advances in miniaturization and performance, this axiom, known as Moore’s Law, has held true since 1965, when Intel co-founder Gordon Moore first made that statement based on emerging trends in chip manufacturing at Intel.

However, integrated circuits are hitting hard physical limits that are rendering Moore’s Law obsolete — elements on a dense integrated circuit (IC) can get only so small and so tightly packed together before they begin to interfere with each other and otherwise lose their functionality.

“Apart from fundamental physical limits to the scaling of transistor feature sizes below a few nanometers, there are significant challenges in terms of reducing power dissipation, as well as justifying the incurred cost of IC fabrication,” said Kaustav Banerjee, a professor of electrical and computer engineering at UC Santa Barbara. As a result, the very devices that we rely on for their steadily improving performance and versatility — computers, smartphones, internet-enabled gadgets — would also hit a limit, he said.

The UCSB Current – "Saving Moore's Law" (full article)