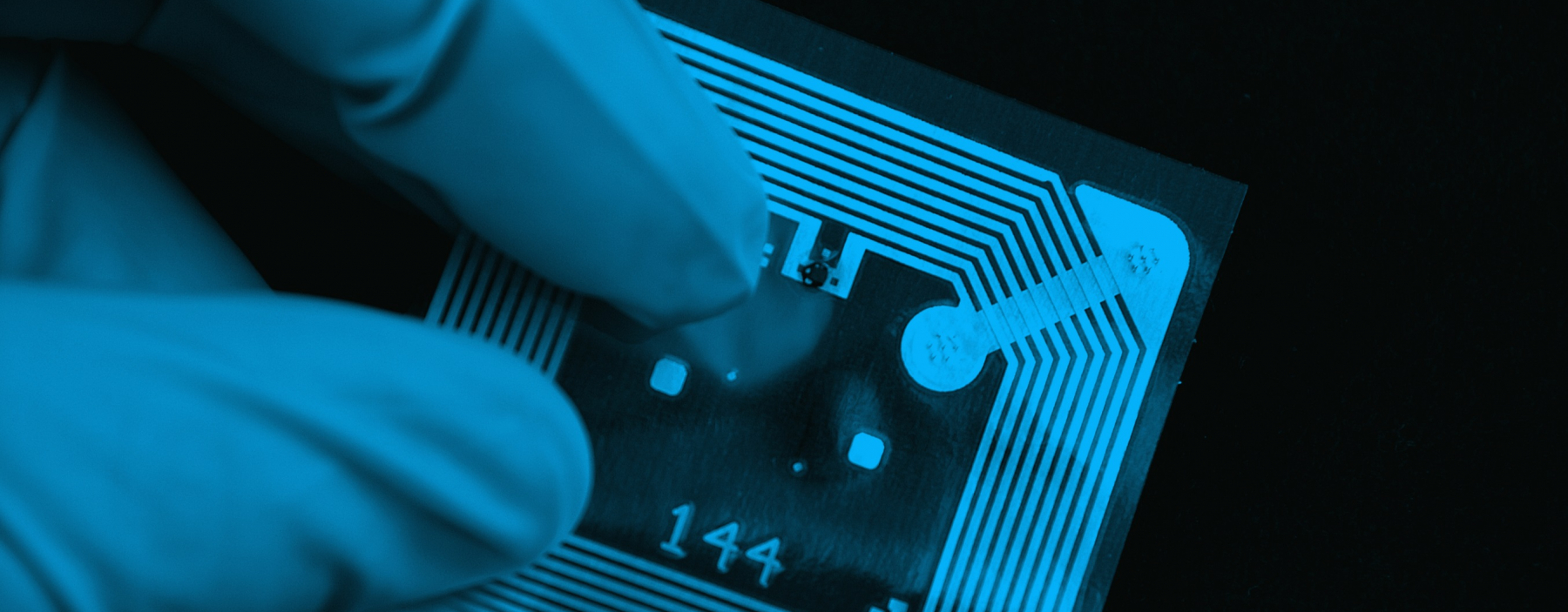

Interconnects and Passives

Emerging interconnect technologies for next-generation ICs; Solutions to interconnect issues in multicore, network-on-chip, neuromorphic, and monolithic 3D ICs; Ultra high-frequency modeling and parasitic extraction techniques for on-chip interconnects and passive elements; RFIDs, inductors, transformers, capacitors, and antennas that exploit new materials and mechanisms for boosting performance and reliability along with area/energy- efficiency and flexibility.

Selected Publications

Junkai Jiang, Jae Hwan Chu and Kaustav Banerjee

IEEE International Electron Devices Meeting (IEDM), San Francisco, December 1-5, 2018, pp. 34.5.1-34.5.4.

One of the two IEDM 2018 papers selected in Research Highlights of Nature Electronics, Nov 30, 2018

Jiahao Kang, Yuji Matsumoto, Xiang Li, Junkai Jiang, Xuejun Xie, Keisuke Kawamoto, Munehiro Kenmoku, Jae Hwan Chu, Wei Liu, Junfa Mao, Kazuyoshi Ueno and Kaustav Banerjee

Nature Electronics, Vol. 1, No. 1, pp. 46-51, 2018.

Read Media Coverage by Forbes

Chuan Xu, Navin Srivastava, Roberto Suaya and Kaustav Banerjee

IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, Vol. 31, No. 11, pp. 1698-1710, 2012.

Chuan Xu, Hong Li, Roberto Suaya and Kaustav Banerjee

IEEE Transactions on Electron Devices, Vol. 57, No. 12, pp. 3405-3417, Dec. 2010.

Hong Li, Chuan Xu, Navin Srivastava, and Kaustav Banerjee

IEEE Transactions on Electron Devices, Special Issue on Compact Interconnect Models for Gigascale Integration, Vol. 56, No. 9, pp. 1799-1821, Sep 2009.

Invited and Highlighted on the Journal Cover